Invited Speakers

A key technology future direction is CMOS + X, where X can be memory, photonics, spintronics, power electronics, nanomechanics, sensors and actuators, RF/mm-wave, and even quantum computing. Nanosystems of 3D integrated “X” technology (N3XT) is a key concept at the chip level. We must also go beyond a single chip from a wafer and focus on integrating chips into systems using MOSAIC (MOnolithic Stacked Assembled IC). I will give an overview of the new materials and device technologies that may need to be developed to realize this vision. In particular, low-dimensional materials are suitable for logic transistors in this 3D MOSAIC of N3XT chips vision because of the low temperature for device fabrication as well as the thin device layers.

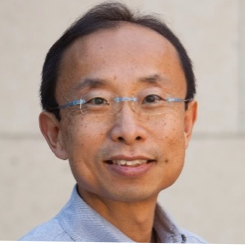

Biography:

H.-S. Philip Wong is the Willard R. and Inez Kerr Bell Professor in the School of Engineering at Stanford University. He joined Stanford University as Professor of Electrical Engineering in September, 2004. From 1988 to 2004, he was with the IBM T.J. Watson Research Center. From 2018 to 2020, he was on leave from Stanford and was the Vice President of Corporate Research at TSMC, the largest semiconductor foundry in the world, and since 2020 remains the Chief Scientist of TSMC. He is a Fellow of the IEEE and received the IEEE Electron Devices Society J.J. Ebers Award, the society’s highest honor to recognize outstanding technical contributions to the field of electron devices that have made a lasting impact. He is the founding Faculty Co-Director of the Stanford SystemX Alliance – an industrial affiliate program focused on building systems, the faculty director of the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI), and the faculty director of the Stanford Nanofabrication Facility.

Friday, April 29, 2022

<p>Plenary</p>

H.-S. Philip Wong - ‘Low dimensional channel materials for logic transistors‘ - Stanford University